# ICB HSMC

# **User Manual**

# **CONTENTS**

| Chapter 1       | Introduction                          | 3  |

|-----------------|---------------------------------------|----|

| 1.1 Features    |                                       | 3  |

| 1.2 About the l | Kit                                   | 4  |

| 1.3 Getting He  | elp                                   | 5  |

| Chapter 2       | ICB Architecture                      | 6  |

| 2.1 Layout and  | l Components                          | 6  |

| 2.2 Block Diag  | gram of the ICB                       | 7  |

| Chapter 3       | Board Components                      | 9  |

| 3.1 HSMC Exp    | pansion Connector                     | 9  |

| 3.2 GPIO Inter  | rface                                 | 12 |

| 3.3 RS-232 Int  | terface                               | 13 |

| 3.4 RS-485 Int  | terface                               | 14 |

| 3.5 CAN Inter   | face                                  | 16 |

| 3.6 PIO Interfa | ace                                   | 16 |

| Chapter 4       | Assembling the ICB                    | 18 |

| 4.1 Assemble l  | ICB with DE2-115                      | 18 |

| 4.2 Generate I  | CB Project via DE2-115 System Builder | 19 |

| Chapter 5       | ICB Demonstrations                    | 25 |

| 5.1 System Re   | quirements                            | 25 |

| 5.2 RS-232 Co   | ommunication                          | 25 |

| 5.3 RS-485 Lo   | oopback Test                          | 27 |

| 5.4 CAN Loop    | back Test                             | 29 |

| Chapter 6       | Appendix                              | 32 |

#### **Industrial Communication Board**

| 6.1 Revision History    | <br>32 |

|-------------------------|--------|

| 6.2 Convright Statement | 32     |

# Introduction

The Industrial Communication Board (ICB-HSMC) is designed to provide common industry standard interfaces for FPGA platforms that support RS-232, RS-485, and CAN connectivity through a High-Speed Mezzanine Connector (HSMC). It allows users to setup a communication network for industrial use through the industrial standard interfaces on the ICB. This board features one RS-232 interface, one GPIO interface, four RS-485 interfaces, two CAN interfaces, and four PIO interfaces. The ICB is an ideal addition to the DE2-115 platform for developing industrial networking solutions on Altera FPGAs.

#### 1.1 Features

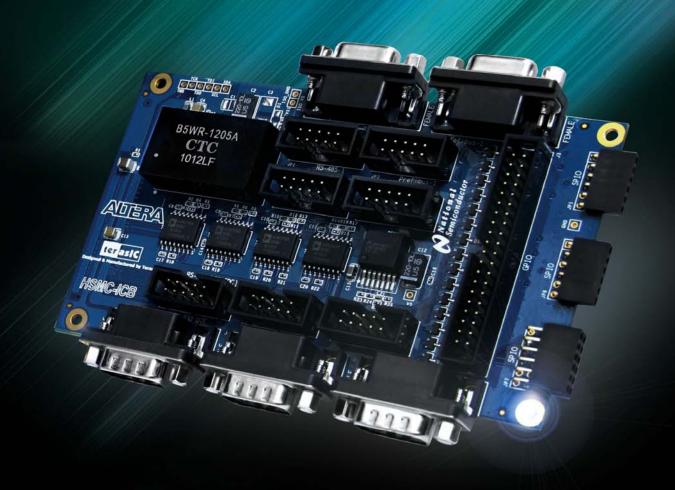

Figure 1-1 shows a photograph of the ICB.

Figure 1-1 Layout of the ICB

The key features of the card are listed below:

- HSMC Connector

- 40-Pin GPIO interface

- o 36 user I/Os

- Two 6-Pin PIO interfaces

- o 4 user I/Os per interface

- 12-Pin PIO interface

- o 8 user I/Os

- RS-232 interface

- o Maxim RS-232 transceiver (MAX3238) support streaming transmission up to 250kbps

- o Complete RS-232 signal interface

- o 1 male DB9 Connector and one 10-pin header (shares pins with DB9 Connector)

- RS-485 interface

- o Analog Device isolated RS-485 transceiver (AMD2486), Profibus compliant

- o Half-duplex transmission with data rate up to 20Mbps

- o 4 channel transceivers, two channels output with DB9 female connectors and 10-pin headers (share pins with DB9), two channels output with 10-pin headers

- CAN interface

- o Maxim Low-Supply-Current CAN transceiver (MAX3051)

- o High speed operation up to 1Mbps

- o 2 male DB9 and two 10-pin headers (share pins with Connectors)

- Power

- o Isolated 5V power supply for RS-485 transceiver bus side

- $\circ$  5V/3.3V power supply

#### 1.2 About the Kit

The kit will come with the following contents:

- ICB-HSMC

- System CD-ROM

The system CD contains technical documents of the ICB, which includes component datasheets, demonstrations illustrating connectivity of the CAN, RS-232 and RS-485 ports, schematic, and user manual.

Figure 1-2 shows the ICB contents.

Figure 1-2 ICB contents

### 1.3 Getting Help

Here is information of how to get help if you encounter any problems:

Terasic Technologies

• Tel: +886-3-550-8800

• Email: <a href="mailto:support@terasic.com">support@terasic.com</a>

# ICB Architecture

This chapter describes the architecture of the ICB including block diagram and components.

#### 2.1 Layout and Components

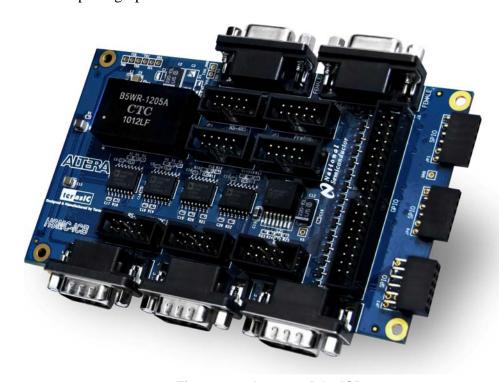

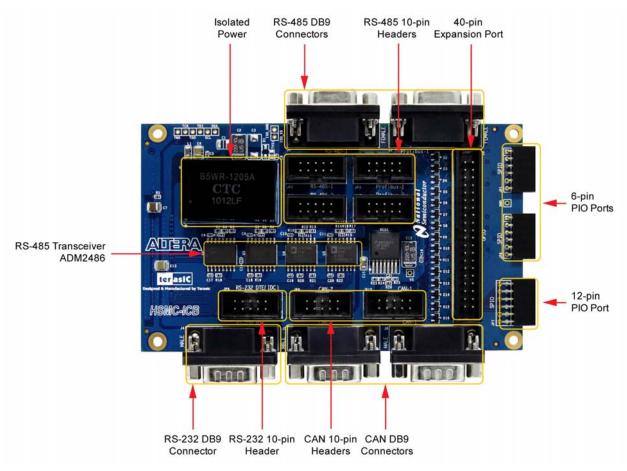

The picture of the ICB is shown in **Figure 2-1** and **Figure 2-2**. It depicts the layout of the board and indicates the locations of the connectors and key components.

Figure 2-1 The ICB-HSMC PCB and component diagram (top view)

Figure 2-2 The ICB-HSMC PCB and component diagram (bottom view)

The following interfaces are provided on the ICB:

- HSMC Connector (J7)

- 40-pin GPIO Header (J3)

- 6-pin Header (JP1/JP6)

- 12-pin Header(JP7)

- 10-pin Header (JP2/JP3/JP4/JP5/JP6/JP9/JP10)

- DB9 Connector (J1/J2/J4/J5/J6)

#### 2.2 Block Diagram of the ICB

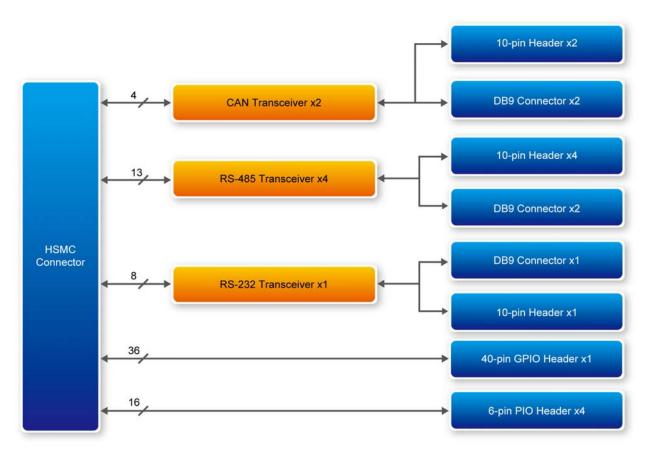

**Figure 2-3** shows the block diagram of the ICB-HSMC. The HSMC connector houses all the wires from peripheral interfaces and makes to the FPGA on the main board.

Figure 2-3 Block diagram of ICB-HSMC

# **Board Components**

This chapter describes the components, connectors, and pin assignments on the ICB.

#### 3.1 HSMC Expansion Connector

The HSMC interface provides a mechanism to extend the peripheral set of an FPGA host board by means of a mezzanine card, which can address today's high speed signaling requirement as well as standard or legacy low-speed device interface support. **Table 3-1** lists the pin assignments of the HSMC connector.

Table 3-1 Pin assignments and descriptions on HSMC connector

| Pin Numbers | Name        | Direction    | Description                  |

|-------------|-------------|--------------|------------------------------|

| 1-32        | -           | -            | -                            |

| 33          | HSMC_SDA    | Input/Output | HSMC serial address/data I/O |

| 34          | HSMC_SCL    | Output       | HSMC serial clock            |

| 35          | HSMC_TCK    | Output       | JTAG clock                   |

| 36          | HSMC_TMS    | Output       | JTAG mode select             |

| 37          | HSMC_TDO    | Input        | JTAG test data out           |

| 38          | HSMC_TDI    | Output       | JTAG test data in            |

| 39          | -           | -            | -                            |

| 40          | -           | -            | -                            |

| 41          | GPIO_DATA34 | Input/Output | GPIO data                    |

| 42          | GPIO_DATA33 | Input/Output | GPIO data                    |

| 43          | GPIO_DATA35 | Input/Output | GPIO data                    |

| 44          | GPIO_DATA32 | Input/Output | GPIO data                    |

| 45          | VCC3P3      | Power        | Power 3.3V                   |

| 46          | VCC12       | Power        | Power 12V                    |

| 47          | GPIO_DATA4  | Input/Output | GPIO data                    |

| 48          | GPIO_DATA0  | Input/Output | GPIO data                    |

| 49          | GPIO_DATA5  | Input/Output | GPIO data                    |

| 50          | GPIO_DATA1  | Input/Output | GPIO data                    |

| 51          | VCC3P3      | Power        | Power 3.3V                   |

| 52          | VCC12       | Power        | Power 12V                    |

| 100       | VCC12       | Power        | Power 12V  |

|-----------|-------------|--------------|------------|

| 99        | VCC3P3      | Power        | Power 3.3V |

| 98        | RS232_DTR   | Input        | RS-232 DTR |

| 97        | RS232_CTS   | Output       | RS-232 CTS |

| 96        | RS232_RTS   | Input        | RS-232 RTS |

| 95        | RS232_RI    | Output       | RS-232 RI  |

| 94        | VCC12       | Power        | Power 12V  |

| 93        | VCC3P3      | Power        | Power 3.3V |

| 92        | GPIO_DATA27 | Input/Output | GPIO data  |

| 91        | GPIO_DATA31 | Input/Output | GPIO data  |

| 90        | GPIO_DATA26 | Input/Output | GPIO data  |

| 89        | GPIO_DATA30 | Input/Output | GPIO data  |

| 88        | VCC12       | Power        | Power 12V  |

| 87        | VCC3P3      | Power        | Power 3.3V |

| 86        | GPIO_DATA25 | Input/Output | GPIO data  |

| 85        | GPIO_DATA29 | Input/Output | GPIO data  |

| 84        | GPIO_DATA24 | Input/Output | GPIO data  |

| 83        | GPIO_DATA28 | Input/Output | GPIO data  |

| 82        | VCC12       | Power        | Power 12V  |

| 81        | VCC3P3      | Power        | Power 3.3V |

| 80        | GPIO_DATA19 | Input/Output | GPIO data  |

| 79        | GPIO_DATA23 | Input/Output | GPIO data  |

| 78        | GPIO_DATA18 | Input/Output | GPIO data  |

| 77        | GPIO_DATA22 | Input/Output | GPIO data  |

| 76<br>    | VCC12       | Power        | Power 12V  |

| <b>75</b> | VCC3P3      | Power        | Power 3.3V |

| 74<br>    | GPIO_DATA17 | Input/Output | GPIO data  |

| 73        | GPIO_DATA21 | Input/Output | GPIO data  |

| 72        | GPIO_DATA16 | Input/Output | GPIO data  |

| 71        | GPIO_DATA20 | Input/Output | GPIO data  |

| 70        | VCC12       | Power        | Power 12V  |

| 69        | VCC3P3      | Power        | Power 3.3V |

| 68        | GPIO_DATA11 | Input/Output | GPIO data  |

| 67        | GPIO_DATA15 | Input/Output | GPIO data  |

| 66        | GPIO_DATA10 | Input/Output | GPIO data  |

| 65        | GPIO_DATA14 | Input/Output | GPIO data  |

| 64        | VCC12       | Power        | Power 12V  |

| 63        | VCC3P3      | Power        | Power 3.3V |

| 62        | GPIO_DATA9  | Input/Output | GPIO data  |

| 61        | GPIO_DATA13 | Input/Output | GPIO data  |

| 60        | GPIO_DATA8  | Input/Output | GPIO data  |

| 59        | GPIO_DATA12 | Input/Output | GPIO data  |

| 58        | VCC12       | Power        | Power 12V  |

| 57        | VCC3P3      | Power        | Power 3.3V |

| 56        | GPIO_DATA3  | Input/Output | GPIO data  |

| 55        | GPIO_DATA7  | Input/Output | GPIO data  |

| 54        | GPIO_DATA2  | Input/Output | GPIO data  |

|           | GPIO_DATA6  | Input/Output |            |

10

| 101 | PIO1_DATA0  | Input/Output | PIO1 data                  |

|-----|-------------|--------------|----------------------------|

| 102 | PIO0 DATA0  | Input/Output | PIO0 data                  |

| 103 | PIO1 DATA1  | Input/Output | PIO1 data                  |

| 104 | PIO0 DATA1  | Input/Output | PIO0 data                  |

| 105 | VCC3P3      | Power        | Power 3.3V                 |

| 106 | VCC12       | Power        | Power 12V                  |

| 107 | PIO1 DATA2  | Input/Output | PIO1 data                  |

| 108 | PIO0 DATA2  | Input/Output | PIO0 data                  |

|     | I IOU_DATAL | mpadoatpat   | 1 100 data                 |

| 109 | PIO1_DATA3  | Input/Output | PIO1 data                  |

| 110 | PIO0_DATA3  | Input/Output | PIO0 data                  |

| 111 | VCC3P3      | Power        | Power 3.3V                 |

| 112 | VCC12       | Power        | Power 12V                  |

| 113 | PIO3_DATA0  | Input/Output | PIO3 data                  |

| 114 | PIO2_DATA0  | Input/Output | PIO2 data                  |

| 115 | PIO3_DATA1  | Input/Output | PIO3 data                  |

| 116 | PIO2_DATA1  | Input/Output | PIO2 data                  |

| 117 | VCC3P3      | Power        | Power 3.3V                 |

| 118 | VCC12       | Power        | Power 12V                  |

| 119 | PIO3_DATA2  | Input/Output | PIO3 data                  |

| 120 | PIO2_DATA2  | Input/Output | PIO2 data                  |

| 121 | PIO3_DATA3  | Input/Output | PIO3 data                  |

| 122 | PIO2_DATA3  | Input/Output | PIO2 data                  |

| 123 | VCC3P3      | Power        | Power 3.3V                 |

| 124 | VCC12       | Power        | Power 12V                  |

| 125 | RS485_2_RXD | Input        | RS-485 channel 2 RXD       |

| 126 | RS485_0_RXD | Input        | RS-485 channel 0 RXD       |

| 127 | RS485_2_TXD | Output       | RS-485 channel 2 TXD       |

| 128 | RS485_0_TXD | Output       | RS-485 channel 0 TXD       |

| 129 | VCC3P3      | Power        | Power 3.3V                 |

| 130 | VCC12       | Power        | Power 12V                  |

| 131 | RS485_2_RTS | Output       | RS-485 channel 2 RTS       |

| 132 | RS485_0_RTS | Output       | RS-485 channel 0 RTS       |

| 133 | RS485_3_RXD | Input        | RS-485 channel 3 RXD       |

| 134 | RS485_1_RXD | Input        | RS-485 channel 1 RXD       |

| 135 | VCC3P3      | Power        | Power 3.3V                 |

| 136 | VCC12       | Power        | Power 12V                  |

| 137 | RS485_3_TXD | Output       | RS-485 channel 3 TXD       |

| 138 | RS485_1_TXD | Output       | RS-485 channel 1 TXD       |

| 139 | RS485_3_RTS | Output       | RS-485 channel 3 RTS       |

| 140 | RS485_1_RTS | Output       | RS-485 channel 1 RTS       |

| 141 | VCC3P3      | Power        | Power 3.3V                 |

| 142 | VCC12       | Power        | Power 12V                  |

| 143 | RS232_DSR   | Output       | RS-232 DSR                 |

| 144 | POWER_VALID | Output       | RS-485 0,1,2,3 power valid |

| 145 | RS232_TXD   | Output       | RS-232 TXD                 |

| 146 | RS232_DCD   | Output       | RS-232 DCD                 |

| 147 | VCC3P3      | Power        | Power 3.3V                 |

| 148 | VCC12     | Power  | Power 12V         |

|-----|-----------|--------|-------------------|

| 149 | CAN1_T    | Output | CAN channel 1 TXD |

| 150 | CAN0_T    | Output | CAN channel 0 TXD |

| 151 | CAN1_R    | Input  | CAN channel 1 RXD |

| 152 | CAN0_R    | Input  | CAN channel 0 RXD |

| 153 | VCC3P3    | Power  | Power 3.3V        |

| 154 | VCC12     | Power  | Power 12V         |

| 155 | -         | -      | -                 |

| 156 | RS232_RXD | Input  | RS-232 RXD        |

| 157 | -         | -      | -                 |

| 158 | -         | -      | -                 |

| 159 | VCC3P3    | Power  | Power 3.3V        |

| 160 | GND       | Power  | Power Ground      |

#### 3.2 GPIO Interface

This section describes the GPIO interface on the ICB

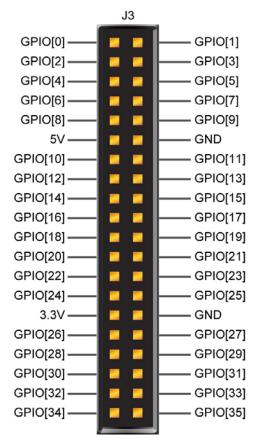

The ICB contains a GPIO interface with a 40-pin header. **Figure 3-1** shows the pin names defined on the GPIO connector used in general purpose applications. For pin mapping information between the GPIO and HSMC connector, please refer to **Table 3-1**, using pin names here as indexes.

Figure 3-1 Pin names defined on GPIO connector

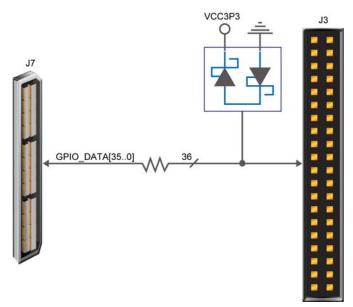

GPIO is widely used for housing various application needs such as video processing or image acquisition, etc. It supports up to 50MHz data rate using a reliable cable connection. Each data pin on the GPIO is connected to an extra protection circuit made up of two clamping diodes and one serial resistor. **Figure 3-2** shows the protection circuitry that is on each of the 36 data pins on the 40-pin header.

Figure 3-2 Protection circuit for data pins on GPIO

#### 3.3 RS-232 Interface

This section describes the RS-232 interface on the ICB-HSMC.

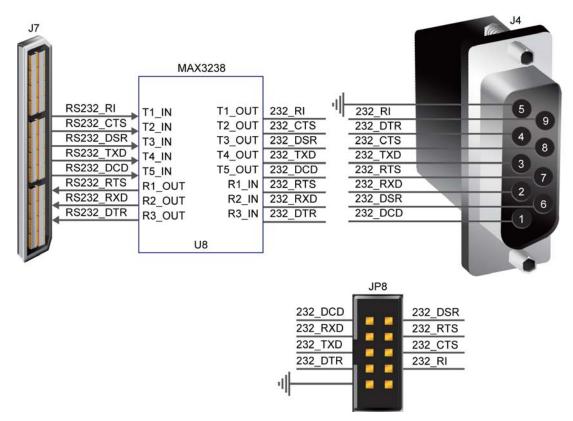

The ICB provides a full featured RS-232 interface using a Maxim 3238 chip with a guaranteed data rate of 250 Kbps. **Figure 3-3** shows the I/O connectors J4 and JP8 for the RS-232 signals.

Figure 3-3 Wiring between the HSMC and RS-232 interface

The male RS-232 connector provides the industrial standard cabling interface, in addition to a 10-pin header used for simple communication conditions where a specific cable is not needed.

#### 3.4 RS-485 Interface

This section describes RS-485 interface on the ICB-HSMC.

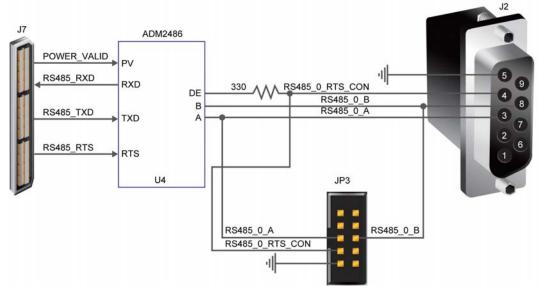

There are four RS-485 links from the HSMC connector to two female DB9 connectors and four 10-pin headers. Two of the 10-pin headers share pins with the two DB9 connectors. Within the four ports, two ports are compliant with the profibus specification and are suitable of using as physical link in industrial multi-terminal control applications. **Figure 3-4** shows the hardware wiring between the HSMC and one RS-485 channel.

Figure 3-4 Wiring between HSMC and RS-485 interface

Table 3-2 gives the pin assignments on 10-pin headers and DB9 connectors for RS-485 signals.

Table 3-2 Pin assignments and descriptions for RS-485 interfaces

| RS-485 Channel      | Signal Name     | 10-pin Header | DB9 connector |

|---------------------|-----------------|---------------|---------------|

| Channel 0 (Profibus | RS485_0_A       | 5(JP3)        | 3(J2)         |

|                     | RS485_0_B       | 6(JP3)        | 8(J2)         |

|                     | RS485_0_RTS_CON | 7(JP3)        | 4(J2)         |

| compliance)*        | VCC5_ISO        | 2(JP3)        | 6(J2)         |

|                     | GND             | 9(JP3)        | 5(J2)         |

|                     | RS485_1_A       | 6(JP2)        | 8(J1)         |

|                     | RS485_1_B       | 5(JP2)        | 3(J1)         |

| Channel 1           | RS485_1_RTS_CON | 7(JP2)        | 4(J1)         |

|                     | VCC5_ISO        | 2(JP2)        | 6(J1)         |

|                     | GND             | 9(JP2)        | 5(J1)         |

|                     | RS485_2_A       | 5(JP5)        | -             |

| Channel 2 (Profibus | RS485_2_B       | 6(JP5)        | -             |

| compliance)*        | RS485_2_RTS_CON | 7(JP5)        | -             |

| compliance)         | VCC5_ISO        | 2(JP5)        | -             |

|                     | GND             | 9(JP5)        | -             |

| Channel 3           | RS485_3_A       | 6(JP4)        | -             |

|                     | RS485_3_B       | 5(JP4)        | -             |

|                     | RS485_3_RTS_CON | 7(JP4)        | -             |

|                     | VCC5_ISO        | 2(JP4)        | -             |

|                     | GND             | 9(JP4)        | -             |

<sup>\*</sup>Note, the Profibus implementation is not fully tested on the ICB.

#### 3.5 CAN Interface

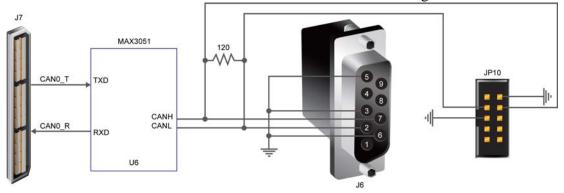

This section describes the CAN interface on the ICB-HSMC.

The board features two CAN links from the HSMC connector to two DB9 male connectors and two 10-pin headers. These two 10-pin headers share the same pins with two DB9 connectors. **Figure 3-5** shows the connections between the HSMC and the CAN interface through a CAN transceiver chip.

Figure 3-5 Wiring between HSMC and CAN interface

Table 3-3 gives the pin assignments on 10-pin headers and DB9 connectors for CAN signals.

| CAN Channel | Signal Name | 10-pin Header | DB9 Connector |

|-------------|-------------|---------------|---------------|

|             | CANH        | 4(JP10)       | 7(J6)         |

| Channel 0   | CANL        | 3(JP10)       | 2(J6)         |

|             | GND         | 2,5(JP10)     | 3,5,6(J6)     |

| Channel 1   | CANH        | 4(JP9)        | 7(J5)         |

|             | CANL        | 3(JP9)        | 2(J5)         |

|             | GND         | 2,5(JP9)      | 3,5,6(J5)     |

Table 3-3 Pin assignments and descriptions for CAN interfaces

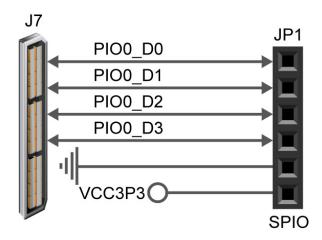

#### 3.6 PIO Interface

This section describes the PIO interface on the ICB-HSMC.

The board has four PIO links from the HSMC connector with two 6-pin ports and one 12-pin port (dual PIO link). The 6-pin PIO port not only provides four general-purpose I/Os but also has one 3.3V power supply and one ground pin. **Figure 3-6** gives the related schematic of the PIO connector.

Figure 3-6 Wiring between HSMC and PIO interface

# Assembling the ICB

This chapter gives instructions for connecting the ICB to versatile host boards.

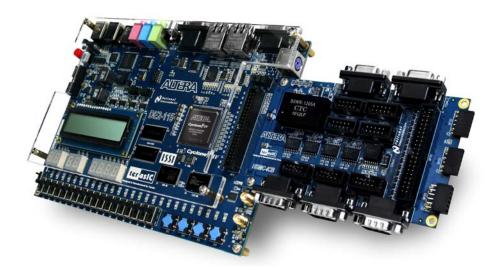

#### 4.1 Assemble ICB with DE2-115

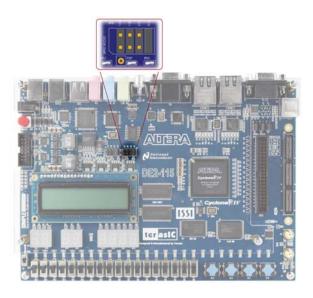

For connecting the ICB to the DE2-115 board, plug the ICB to the HSMC 'socket' (JP8) of the DE2-115 board. Users could additionally screw on and tighten the connection for extra mechanical stability. **Figure 4-1** shows the assembled hardware.

Figure 4-1 Assembling ICB with DE2-115 board

Note that the ICB is designed to use the 3.3V or 2.5V I/O signaling standard. Before powering on the DE2-115 board, set the desired I/O standard for the HSMC connector. **Figure 4-2** shows the header for setting the HSMC power supply voltage.

Figure 4-2 HSMC VCCIO supply voltage setting header (JP7)

#### 4.2 Generate ICB Project via DE2-115 System Builder

The DE2-115 board comes with a useful utility that helps users generate top level design and pin assignment files that include specific HSMC daughter card information. The automatically generated top level design and Quartus II setting file eliminate potential common mistakes encountered when manually typing in the signal wires between DE2-115 and daughter card.

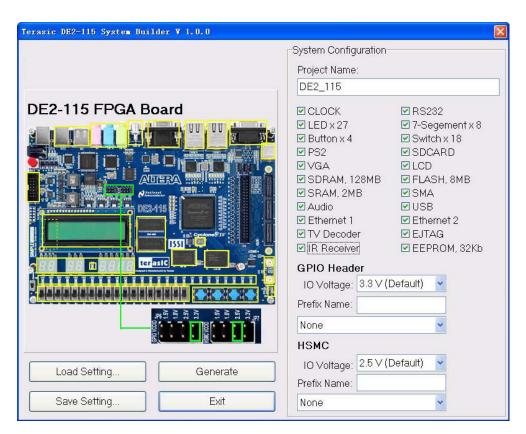

#### ■ Install and launch the DE2-115 System Builder

The DE2-115 System Builder is available from the DE2-115 system CD-ROM, under the DE2\_115\_tools folder. Users can copy the entire folder to a host PC without installing the utility. Before using the DE2-115 System Builder, execute the DE2\_115\_SystemBuilder.exe on the host computer as shown in **Figure 4-3**.

Figure 4-3 The DE2-115 System Builder window

#### **■** Input Project Name

Input project name as show in Figure 4-4.

Project Name: Type in an appropriate name here, it will automatically be assigned as the name of your top-level design entity.

Figure 4-4 The DE2-115 Board Type and Project Name

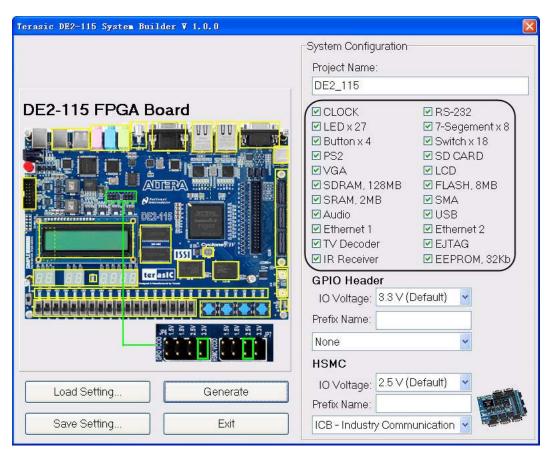

#### **■** System Configuration

Under System Configuration, users can enable the desired components on the FPGA host board as shown in **Figure 4-5**. If the component is enabled, the DE2-115 System Builder will automatically generate the associated pin assignments, including the pin names, pin locations, pin directions, and I/O standards.

Figure 4-5 System Configuration Group

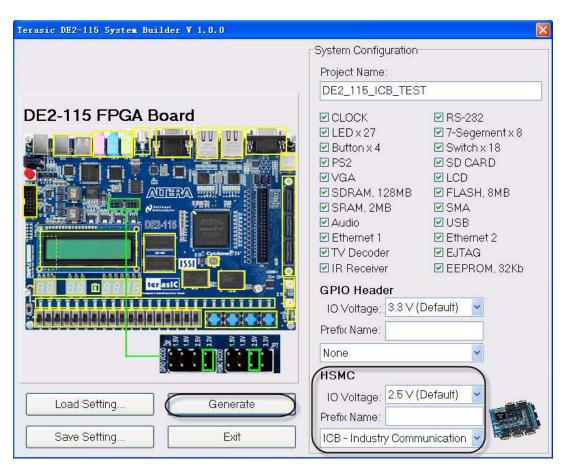

#### **■ HSMC Expansion**

**Figure 4-6** illustrates the usage of the DE2-115 System Builder specifying ICB connecting to the HSMC interface. This will automatically generate wiring connections between the host board and ICB-HSMC.

Figure 4-6 HSMC Expansion Group

The "Prefix Name" is an optional feature that denotes the pin name of the daughter card assigned in your design. Users may leave this field empty.

**Figure 4-7** illustrates the generated top level design file contains information on the ICB-HSMC connections.

| input  |        | CANO R;      |                                            |

|--------|--------|--------------|--------------------------------------------|

| output |        | CANO T;      |                                            |

| input  |        | CAN1 R;      |                                            |

| output |        | CAN1 T;      |                                            |

| inout  | [35:0] | GPIO DATA;   |                                            |

| inout  | [3:0]  | PIOO DATA;   |                                            |

| inout  | [3:0]  | PIO1 DATA;   |                                            |

| inout  | [3:0]  | PIO2 DATA;   |                                            |

| inout  | [3:0]  | PIO3 DATA;   |                                            |

| output |        | POWER_VALID; |                                            |

| output |        | RS232 CTS;   |                                            |

| output |        | RS232 DCD;   |                                            |

| output |        | RS232 DSR;   | Automatically gonerated wiring information |

| input  |        | RS232 DTR;   | Automatically generated wiring information |

| output |        | RS232 RI;    | between host board and ICB                 |

| input  |        | RS232 RTS;   |                                            |

| input  |        | RS232_RXD;   |                                            |

| output |        | RS232_TXD;   |                                            |

| output |        | RS485 0 RTS; |                                            |

| input  |        | RS485_0_RXD; |                                            |

| output |        | RS485_0_TXD; |                                            |

| output |        | RS485_1_RTS; |                                            |

| input  |        | RS485_1_RXD; |                                            |

| output |        | RS485_1_TXD; |                                            |

| output |        | RS485_2_RTS; |                                            |

| input  |        | RS485_2_RXD; |                                            |

| output |        | RS485_2_TXD; |                                            |

| output |        | RS485_3_RTS; |                                            |

| input  |        | RS485_3_RXD; |                                            |

| output |        | RS485 3 TXD; |                                            |

Figure 4-7 Top level design file includes ICB-HSMC information

24

# ICB Demonstrations

This chapter mainly depicts how to use the ICB through a set of demonstrations located on the software CD. From running the demonstrations, users will know how to implement codes on the DE2-115 for controlling the ICB-HSMC. The demos include communication between RS-232 and PC, RS-485 loopback test, and CAN loopback test.

#### 5.1 System Requirements

Here are boards and connecting wires used to run the demonstrations:

- DE2-115 board 1

- ICB-HSMC

- RS232 cable (DB9 female-female cross cable)

- Connecting wires 4

#### 5.2 RS-232 Communication

This demonstration illustrates how to construct a communication channel between a PC and RS-232 port on the ICB card. Set up of the RS-232 port as follows:

Baud rate: 9600 bpsData bits: 8 bitsStop bit: none

• Parity check bit: 1 bit

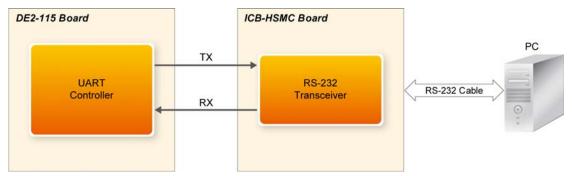

The demonstration also provides PC-side UART terminal communication software using the above parameters. The software running on the PC transmits characters out to the RS-232 port on ICB. Through the HSMC connector, the UART controller implemented on the DE2-115 board buffers the received characters and then sends back to the RS-232 link. The terminal software on PC side senses the receive channel and displays the information in a software window. The system block diagram is shown in **Figure 5-1**.

25

Figure 5-1 Block diagram of RS-232 communication

#### **■** Demonstration source code

Project Directory: \Demonstrations\DE2\_115\_ICB\_RS232

• Bit Stream Used: DE2\_115\_ICB\_RS232.sof

#### **■** PC terminal software

Software Directory: \Demonstrations\DE2 115 ICB RS232\SW

• Executable File : UartTerminal.exe

#### ■ Demonstration batch file

• Batch File Folder: \Demonstrations\DE2\_115\_ICB\_RS232\demo\_batch

• Batch File: DE2 115 ICB RS232.bat, test bashrc

• FPGA Configuration File: DE2\_115\_ICB\_RS232.sof

#### **■** Demonstration setup:

- Assemble the ICB with the DE2-115.

- Power on the DE2-115 board. The green LED (D40) near the HSMC connector will indicate a valid connection.

- Connect the DE2-115 to the PC using the USB-Blaster cable and then run the demo batch DE2\_115\_ICB\_RS232.bat under the \Demonstrations\ DE2\_115\_ICB\_RS232\demo\_ batch\ folder.

- Connect the RS-232 port on the ICB to the PC using a DB9 female-to-female cross cable (Tx and Rx lines are cross connected on two headers to form a peer-to-peer connection).

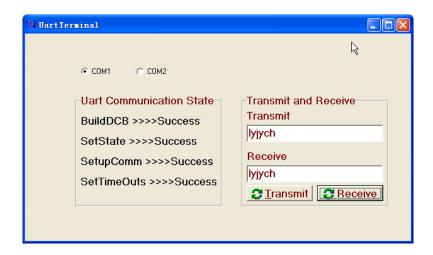

- Run the UartTerminal.exe on the PC, and then select COM1 as the transceiver channel. The software will initiate COM1 and display the success information as shown in **Figure 5-2**.

- Input characters for transmission in the edit box and then press Transmit.

- Press Receive for showing the received data.

Figure 5-2 Terminal software interface

#### 5.3 RS-485 Loopback Test

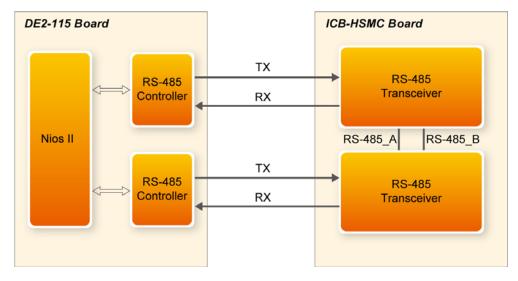

This demonstration illustrates a loopback test through RS-485 interfaces using the UART protocol. Channel 0 of the RS-485 interface (marked as Profibus-1) connects to RS-485 channel 1. Software running on Nios II will first set channel 0 on transmit state and channel 1 on receive state, then it initiates one data transfer with its content set by SW7-0 through channel 0. Once the data is received by the RS-485 controller on channel 1 side, software will set channel 1 on transmit state and channel 0 on receive state then sends data back to the loop. The RS-485 controller on channel 0 side finally gets the passed back data and compares it to the original data. The same procedure will be carried out for channel 2 and 3 except transmit data is set by SW15-8. The result will be indicated on HEX3-0 and HEX7-4 as well as Nios II IDE. **Figure 5-3** shows the block diagram of the test system.

Figure 5-3 Block diagram of the RS-485 loopback test

#### **■** Demonstration source code

- Project Directory: \Demonstrations\ DE2\_115\_ICB\_RS485

- Bit Stream Used: DE2\_115\_ICB\_RS485.sof

- NIOS II Workspace: \Demonstrations\ DE2\_115\_ICB\_RS485\software

#### **■** Demonstration batch file

- Batch File Folder: \Demonstrations\DE2\_115\_ICB\_RS485\demo\_batch

- Batch File: DE2 115 ICB RS485.bat, test bashrc

- FPGA Configuration File: DE2\_115\_ICB\_RS485.sof

#### **■ Demonstration setup:**

- Connect ICB to DE2-115.

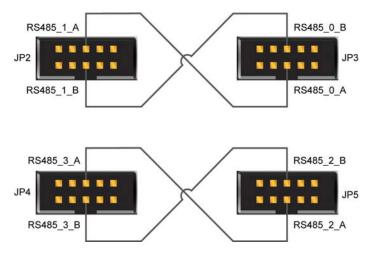

- Establish the loopback by connecting RS-485 channel 0 with channel 1. Note profibus ports (JP3, JP5) have wires A & B swapped. **Figure 5-4** shows the wiring diagram for two loops.

- Power on DE2-115 board. Validate the connection by examining the status of the green LED near the HSMC connector.

- Change the transmit contents by setting the values of SW7-0 for loop pair 1(channel 0 and 1), SW15-8 for loop pair 2(channel 2 and 3).

- Connect the DE2-115 to the PC using USB-Blaster cable, and execute DE2\_115\_ICB\_RS485.bat under the \Demonstrations\ DE2\_115\_ICB\_RS485\demo\_batch\ folder.

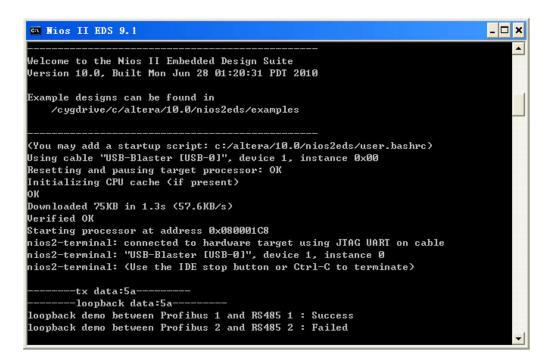

- The prompt window will give test result information as shown in **Figure 5-5**.

- On the DE2-115 board, HEX3-0 indicates loopback information between channel 0 and 1. HEX7-4 indicates loopback information between channel 2 and 3. **Table 5-1** depicts the information indicated on the HEXs.

Figure 5-4 Wiring for the RS-485 loopbacks

Figure 5-5 Test results on the prompt window

Table 5-1 Loopback test result on HEXs for RS-485

| Test Pass Info.           | Test failed info. |

|---------------------------|-------------------|

| S- <test data*=""></test> | FAIL              |

<sup>\*</sup>test data represents the value set by SW15-8 or SW7-0.

#### 5.4 CAN Loopback Test

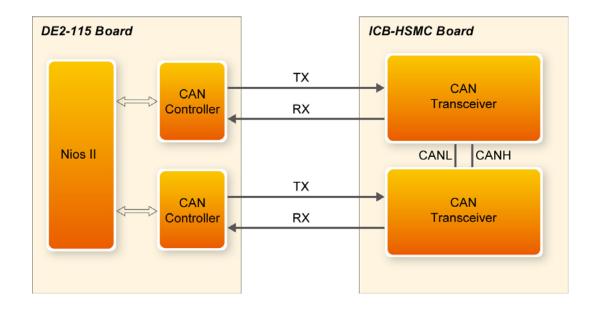

This demonstration illustrates how to construct a communication loop between two CAN interfaces where one initiates the data transfer and the other receives data then sends it back to the loop. SW7-0 is used to set up the transmit data contents. The data loopback flow for CAN is the same as RS-485. In this demonstration, the Nios II processor in the FPGA on the DE2-115 board takes charge of the control work and gives the test result information. The block diagram of the CAN loopback test is as shown in **Figure 5-6**.

Figure 5-6 Block diagram of CAN loopback test

#### **■** Demonstration source code

- Project Directory: \Demonstrations\ DE2\_115\_ICB\_CAN

- Bit Stream Used: DE2\_115\_ICB\_CAN.sof

- NIOS II Workspace: \Demonstrations\ DE2\_115\_ICB\_CAN\software

#### **■** Demonstration batch file

- Batch File Folder: \Demonstrations\DE2\_115\_ICB\_ CAN\ demo\_batch

- Batch File: DE2\_115\_ICB\_ CAN.bat, test\_bashrc

- FPGA Configuration File: DE2\_115\_ICB\_ CAN.sof

- NIOS II Program: DE2\_115\_ICB\_ CAN.elf

#### **■** Demonstration setup:

- Connect ICB to DE2-115.

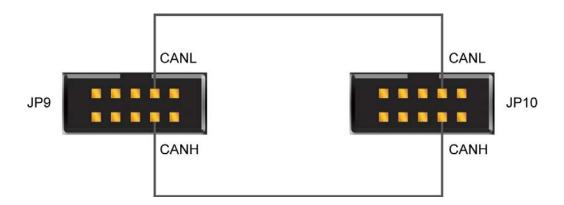

- Connect 'H' and 'L' wire of CAN 0 and CAN1 respectively. **Figure 5-7** shows the wiring manner for the CAN loopback test.

- Power on DE2-115 board. Validate the connection by examining the status of the green LED near the HSMC connector.

- Set the transmitting data for the loop by toggling SW7-0.

- Execute the DE2\_115\_ICB\_CAN.bat in the \Demonstrations\ DE2\_115\_ICB\_CAN \demo batch\ folder.

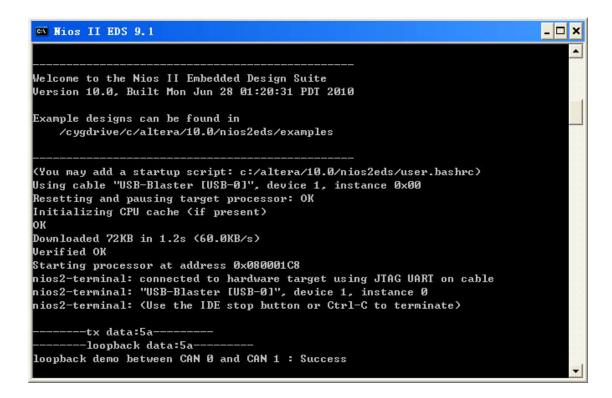

- The prompt window will display the test result information as shown in **Figure 5-8**.

- HEX3-0 on the DE2-115 also prints out the loopback test information. **Table 5-2** depicts the information indicated on the HEXs.

Figure 5-7 Wiring for CAN loopback test

Figure 5-8 Prompt information while running the test

Table 5-2 Loopback test result on HEXs for CAN

| Test Pass Info.           | Test failed info. |

|---------------------------|-------------------|

| S- <test data*=""></test> | FAIL              |

<sup>\*</sup>test data represents the value set by SW7-0.

# Appendix

### 6.1 Revision History

| Version | Change Log                    |

|---------|-------------------------------|

| V1.0    | Initial Version (Preliminary) |

### 6.2 Copyright Statement

Copyright © 2010 Terasic Technologies. All rights reserved.